#### Xilinx ISE 7 Software Manuals and Help - PDF Collection

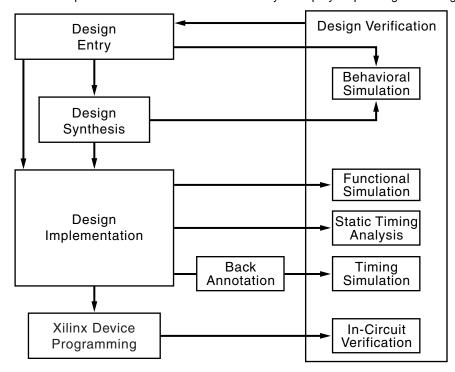

These software documents support the Xilinx<sup>®</sup> Integrated Software Environment (ISE) software. Click a document title on the left to view a document, or click a design step in the following figure to list the documents associated with that step.

**Note:** To get started with the software, see "Getting Started." Manuals provide reference information. Help provides reference information and procedures for Graphical User Interfaces. Tutorials walk you step by step through the design process.

**Note:** Spartan-3L design elements are identical to Spartan-3 design elements. If you are designing a Spartan-3L device, refer to the Spartan-3 design elements in the Libraries Guide.

## **Getting Started**

| Title                    | Summary                                                                                                                                                                                                                                                                   |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISE Help                 | <ul> <li>Provides an overview of the Xilinx<sup>®</sup> Integrated Software Environment<br/>(ISE), including design flow information</li> </ul>                                                                                                                           |

|                          | <ul> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul> |

| ISE Quick Start Tutorial | <ul> <li>Explains how to use VHDL and schematic design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                        |

## **Design Entry**

| Title                                                                                                                            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ChipScope Documentation  Note: ChipScope Pro is one of the Optional Design Tools that can be purchased by clicking Online Store. | <ul> <li>Explains how to use the ChipScope™ Pro Core Generator™ tool to generate ChipScope Pro cores and add them to an FPGA design</li> <li>Explains how to use the ChipScope Pro Core Inserter tool to insert cores into a post-synthesis netlist without disturbing the hardware description language (HDL) source code</li> <li>Explains how to use the ChipScope Pro Analyzer tool to perform incircuit verification (also known as on-chip debugging), including how to view data and interact with ChipScope Pro cores, how to create bitstreams that are compatible with the ChipScope Pro JTAG download function, and how to download bitstreams to an FPGA using JTAG</li> </ul> |

| CORE Generator Help                                                                                                              | <ul> <li>Describes how to use the CORE Generator™ graphical user interface</li> <li>Explains how to customize Xilinx® cores and to add them to your design</li> <li>Explains how to use cores in schematic, VHDL, and Verilog design flows</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EDK Supplemental Information                                                                                                     | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze™ and the IBM® PowerPC® processors</li> <li>Includes information on core templates and Xilinx® device drivers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Hardware User Guides                                                                                                             | <ul> <li>Describes the function and operation of Virtex™-II and Virtex-II Pro™ devices, including information on the RocketIO™ transceiver and IBM® PowerPC® processor</li> <li>Describes how to achieve maximum density and performance using the special features of the devices</li> <li>Includes information on FPGA configuration techniques and printed circuit board (PCB) design considerations</li> </ul>                                                                                                                                                                                                                                                                         |

| ISE Help                                                                                                                         | <ul> <li>Provides an overview of the Xilinx® Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul>                                                                                                                                                                                                                                                                                            |

| ISE Text Editor Help                                                                                                             | Explains how to use the ISE Text Editor to create, view, and edit source files and other text files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ISE Quick Start Tutorial                                                                                                         | <ul> <li>Explains how to use VHDL and schematic design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Next Page >>

## **Design Entry (continued)**

| Title                                               | Summary                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Libraries Guide                                     | • Includes Xilinx <sup>®</sup> Unified Library information arranged by slice count, supported architectures, and functional categories                                                                                                                                                                                               |

|                                                     | <ul> <li>Describes each Xilinx design element, including supported architectures, usage information, syntax examples, and related constraints</li> <li>Includes Spartan-II/IIE/3, Virtex/E/II/II-Pro/II-ProX, XC9500, CoolRunner-II/XPLA3</li> </ul>                                                                                 |

|                                                     | <b>Note:</b> Spartan-3L design elements are identical to Spartan-3 design elements. If you are designing a Spartan-3L device, refer to the Spartan-3 design elements in the Libraries Guide.                                                                                                                                         |

| PACE Help                                           | <ul> <li>Explains how to use the Pinout and Area Constraints Editor (PACE) graphical user interface to define legal pin assignments and to create properly sized area constraints</li> <li>Includes information on how to create non-rectangular areas</li> </ul>                                                                    |

| RTL and Technology Viewer Help                      | Explains how to use the RTL and Technology Viewers to view schematic netlists                                                                                                                                                                                                                                                        |

| Schematic and Symbol Editor<br>Help                 | Explains how to use the Schematic and Symbol Editors to create, view, and edit schematics and symbols                                                                                                                                                                                                                                |

| Spartan-3E Libraries Guide for<br>HDL Designs       | <ul> <li>Includes a general description of the Spartan-3E™ architecture</li> <li>Includes a list of all Spartan-3E design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul> |

| Spartan-3E Libraries Guide for<br>Schematic Designs | <ul> <li>Includes a general description of the Spartan-3E architecture</li> <li>Includes a list of all of the Spartan-3E design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                   |

| StateCAD Help                                       | <ul> <li>Explains how to use the StateCAD graphical user interface to create state diagrams and output them to HDL code</li> <li>Explains how to use StateBench, the FSM, Logic, Design, and Optimization Wizards, and the HDL Browser</li> </ul>                                                                                    |

| Synthesis and Verification Design<br>Guide          | <ul> <li>Explains how to use HDLs to design FPGA devices with an emphasis on synthesis and simulation</li> <li>Contains generic examples for tools other than Synopsys<sup>®</sup> tools</li> </ul>                                                                                                                                  |

| System Generator for DSP                            | <ul> <li>Explains the System Generator DSP development environments;<br/>MATLAB and Simulink.</li> <li>Describes how to design, simulate, implement and debug high performance FPGA-based DSP systems.</li> </ul>                                                                                                                    |

Next Page >>

# **Design Entry (continued)**

| Title                            |   | Summary                                                                                                                                               |

|----------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Virtex-4 Libraries Guide for HDL | • | Includes a general description of the Virtex-4 architecture                                                                                           |

| Designs                          | • | Includes a list of all Virtex-4 design elements that can be instantiated using VHDL or Verilog code organized by functional categories                |

|                                  | • | Includes examples of code that can be cut and pasted into a design using a text editor                                                                |

| Virtex-4 Libraries Guide for     | • | Includes a general description of the Virtex-4 architecture                                                                                           |

| Schematic Designs                | • | Includes a list of all of the Virtex-4 design elements for which schematic symbols are available, organized by their respective functional categories |

## **Design Synthesis**

| Title                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDK Supplemental Information               | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze™ and the IBM® PowerPC® processors</li> <li>Includes information on core templates and Xilinx® device drivers</li> </ul>                                                                                                                                           |

| ISE Help                                   | <ul> <li>Provides an overview of the Xilinx® Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul> |

| ISE Quick Start Tutorial                   | <ul> <li>Explains how to use VHDL and schematic design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                                                                                              |

| Synthesis and Verification Design<br>Guide | <ul> <li>Explains how to use HDLs to design FPGA devices with an emphasis on synthesis and simulation</li> <li>Contains generic examples for tools other than Synopsys<sup>®</sup> tools</li> </ul>                                                                                                                                                                                             |

| Xilinx/Synopsys Interface Guide            | <ul> <li>Describes the interface between Xilinx® and Synopsys® Design Compiler®, FPGA Compiler, and FPGA Compiler II<sup>TM</sup></li> <li>Provides information for synthesizing and simulating designs</li> </ul>                                                                                                                                                                              |

| XST User Guide                             | <ul> <li>Explains how to use Xilinx Synthesis Technology (XST) synthesis tool, and how it supports HDL languages, Xilinx® devices, and constraints</li> <li>Explains FPGA and CPLD optimization techniques</li> <li>Describes how to run XST from the Project Navigator Process window and command line</li> </ul>                                                                              |

## **Design Implementation**

| Title                                 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Constraints Editor Help               | <ul> <li>Explains how to use the Constraints Editor graphical user interface to create and modify the most commonly used constraints</li> <li>Includes information on creating constraints groups and on setting constraints</li> </ul>                                                                                                                                                                                                                                                                                               |

| Constraints Guide                     | <ul> <li>Describes each Xilinx<sup>®</sup> constraint, including supported architectures, applicable elements, propagation rules, and syntax examples</li> <li>Describes constraint types and constraint entry methods</li> <li>Provides strategies for using timing constraints</li> <li>Describes supported third party constraints</li> </ul>                                                                                                                                                                                      |

| Development System<br>Reference Guide | <ul> <li>Describes Xilinx® implementation tools and design flows, including the hierarchical flows such as Incremental Design, Modular Design, and Partial Reconfiguration.</li> <li>Includes reference information for Xilinx FPGA and CPLD command line tools, including syntax, input files, output files, and options.</li> <li>Note: For information on design implementation, see the "NGDBuild," "MAP," "PAR," and "BitGen" chapters for FPGAs, and see the "NGDBuild," "CPLDFit," and "HPrep6" chapters for CPLDs.</li> </ul> |

| EDK Supplemental Information          | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze<sup>TM</sup> and the IBM<sup>®</sup> PowerPC<sup>®</sup> processors</li> <li>Includes information on core templates and Xilinx<sup>®</sup> device drivers</li> </ul>                                                                                                                                                                                                                                    |

| Floorplanner Help                     | <ul> <li>Explains how to use the Floorplanner graphical user interface to floorplan your design</li> <li>Includes information on creating relationally placed macro (RPM) cores, editing constraints, cross-probing to the Timing Analyzer, and placing ports for Modular Design</li> </ul>                                                                                                                                                                                                                                           |

Next Page >>

## **Design Implementation (continued)**

| Title                    | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA Editor Help         | <ul> <li>Explains how to use the FPGA Editor graphical user interface to manually place and route your FPGA design</li> <li>Includes information on adding probes to your design and working with Integrated Logic Analyzer (ILA) cores and cross-probing with Timing Analyzer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |

| iMPACT Help              | <ul> <li>Explains how to use the iMPACT graphical user interface</li> <li>Describes how to download bitstreams to an FPGA or CPLD using a Xilinx Parallel Cable III, Parallel Cable IV, MultiLINX™ Cable, Platform Cable USB, or MultiPRO Desktop Tool</li> <li>Describes how to read back and verify design configuration data and how to perform functional tests on any device</li> <li>Describes how to generate programmable read-only memory (PROM) programming files and programming files using Xilinx System ACE™, a configuration environment that allows space-efficient, pre-engineered, high-density configuration solutions for systems with multiple FPGAs</li> </ul> |

| ISE Help                 | <ul> <li>Provides an overview of the Xilinx® Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul>                                                                                                                                                                                                                                                                                      |

| ISE Quick Start Tutorial | <ul> <li>Explains how to use VHDL and schematic design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Timing Analyzer Help     | <ul> <li>Explains how to use the Timing Analyzer graphical user interface to perform static timing analysis on FPGA and CPLD designs</li> <li>Includes information on evaluating and generating custom timing analysis reports, cross-probing with synthesis tools and the Floorplanner graphical user interface, and using timing and constraint improvement wizards to improve design performance</li> </ul>                                                                                                                                                                                                                                                                       |

| XPower Help              | Explains how to use the XPower application and batch programs to<br>analyze power consumption for Xilinx FPGAs and CPLDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### **Behavioral Simulation**

| Title                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CORE Generator Help                        | <ul> <li>Describes how to use the CORE Generator™ graphical user interface</li> <li>Explains how to customize Xilinx® cores and to add them to your design</li> <li>Explains how to use cores in schematic, VHDL, and Verilog design flows</li> </ul>                                                                                                                                           |

| EDK Supplemental Information               | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze™ and the IBM® PowerPC® processors</li> <li>Includes information on core templates and Xilinx® device drivers</li> </ul>                                                                                                                                           |

| ISE Help                                   | <ul> <li>Provides an overview of the Xilinx® Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul> |

| ISE Simulator Help                         | <ul> <li>Provides an overview of the ISE Simulator.</li> <li>Explains how to create a testbench and simulate the behavior of a design.</li> </ul>                                                                                                                                                                                                                                               |

| ISE Quick Start Tutorial                   | <ul> <li>Explains how to use VHDL and schematic design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                                                                                              |

| Synthesis and Verification Design<br>Guide | <ul> <li>Explains how to use HDLs to design FPGA devices with an emphasis on synthesis and simulation</li> <li>Contains generic examples for tools other than Synopsys<sup>®</sup> tools</li> </ul>                                                                                                                                                                                             |

### **Functional Simulation**

| Title                                             | Summary                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDK Supplemental Information                      | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze™ and the IBM® PowerPC® processors</li> <li>Includes information on core templates and Xilinx® device drivers</li> </ul>                                                                                                                                                      |

| ISE Help                                          | <ul> <li>Provides an overview of the Xilinx<sup>®</sup> Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul> |

| ISE Simulator Help                                | <ul> <li>Provides an overview of the ISE Simulator.</li> <li>Explains how to create a testbench and simulate the behavior of a design.</li> </ul>                                                                                                                                                                                                                                                          |

| ISE Quick Start Tutorial                          | <ul> <li>Explains how to use VHDL and schematic design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                                                                                                         |

| Libraries Guide                                   | <ul> <li>Includes Xilinx® Unified Library information arranged by slice count, supported architectures, and functional categories</li> <li>Describes each Xilinx design element, including supported architectures, usage information, syntax examples, and related constraints</li> </ul>                                                                                                                 |

| Synthesis and Verification Design<br>Guide        | <ul> <li>Explains how to use HDLs to design FPGA devices with an emphasis on synthesis and simulation</li> <li>Contains generic examples for tools other than Synopsys<sup>®</sup> tools</li> </ul>                                                                                                                                                                                                        |

| Virtex-4 Libraries Guide for HDL<br>Designs       | <ul> <li>Includes a general description of the Virtex-4 architecture</li> <li>Includes a list of all Virtex-4 design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul>                                                                            |

| Virtex-4 Libraries Guide for<br>Schematic Designs | <ul> <li>Includes a general description of the Virtex-4 architecture</li> <li>Includes a list of all of the Virtex-4 design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                                                                                             |

## **Static Timing Analysis**

| Title                                 | Summary                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Development System<br>Reference Guide | Describes Xilinx® implementation tools and design flows, including the hierarchical flows such as Incremental Design, Modular Design, and Partial Reconfiguration.                                                                                                                                                                                                                                             |

|                                       | <ul> <li>Includes reference information for Xilinx FPGA and CPLD command line<br/>tools, including syntax, input files, output files, and options.</li> </ul>                                                                                                                                                                                                                                                  |

|                                       | <b>Note:</b> For information on static timing analysis, see the "TRACE" chapter for FPGAs, and see the "TAEngine" chapter for CPLDs. Also, see the "NetGen" chapter.                                                                                                                                                                                                                                           |

| ISE Help                              | <ul> <li>Provides an overview of the Xilinx<sup>®</sup> Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul>     |

| Timing Analyzer Help                  | <ul> <li>Explains how to use the Timing Analyzer graphical user interface to perform static timing analysis on FPGA and CPLD designs</li> <li>Includes information on evaluating and generating custom timing analysis reports, cross-probing with synthesis tools and the Floorplanner graphical user interface, and using timing and constraint improvement wizards to improve design performance</li> </ul> |

## **Timing Simulation**

| Title                                             | Summary                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Constraints Editor Help                           | <ul> <li>Explains how to use the Constraints Editor graphical user interface to create and modify the most commonly used constraints</li> <li>Includes information on creating constraints groups and on setting constraints</li> </ul>                                                                                                                                                                             |

| Development System<br>Reference Guide             | <ul> <li>Describes Xilinx® implementation tools and design flows, including the hierarchical flows such as Incremental Design, Modular Design, and Partial Reconfiguration.</li> <li>Includes reference information for Xilinx FPGA and CPLD command line tools, including syntax, input files, output files, and options.</li> <li>Note: See the "NetGen" chapter for information on timing simulation.</li> </ul> |

| EDK Supplemental Information                      | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze™ and the IBM® PowerPC® processors</li> <li>Includes information on core templates and Xilinx® device drivers</li> </ul>                                                                                                                                                               |

| ISE Help                                          | <ul> <li>Provides an overview of the Xilinx® Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul>                     |

| ISE Quick Start Tutorial                          | <ul> <li>Explains how to use VHDL and schematic design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                                                                                                                  |

| Libraries Guide                                   | <ul> <li>Includes Xilinx® Unified Library information arranged by slice count, supported architectures, and functional categories</li> <li>Describes each Xilinx design element, including supported architectures, usage information, syntax examples, and related constraints</li> </ul>                                                                                                                          |

| Virtex-4 Libraries Guide for HDL<br>Designs       | <ul> <li>Includes a general description of the Virtex-4 architecture</li> <li>Includes a list of all Virtex-4 design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul>                                                                                     |

| Virtex-4 Libraries Guide for<br>Schematic Designs | <ul> <li>Includes a general description of the Virtex-4 architecture</li> <li>Includes a list of all of the Virtex-4 design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                                                                                                      |

### **In-Circuit Verification**

| Title                                                                                                                            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ChipScope Documentation  Note: ChipScope Pro is one of the Optional Design Tools that can be purchased by clicking Online Store. | <ul> <li>Explains how to use the ChipScope™ Pro Core Generator™ tool to generate ChipScope Pro cores and add them to an FPGA design</li> <li>Explains how to use the ChipScope Pro Core Inserter tool to insert cores into a post-synthesis netlist without disturbing the hardware description language (HDL) source code</li> <li>Explains how to use the ChipScope Pro Analyzer tool to perform incircuit verification (also known as on-chip debugging), including how to view data and interact with ChipScope Pro cores, how to create bitstreams that are compatible with the ChipScope Pro JTAG download function, and how to download bitstreams to an FPGA using JTAG</li> </ul> |

| ISE Help                                                                                                                         | <ul> <li>Provides an overview of the Xilinx® Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul>                                                                                                                                                                                                                                                                                            |

### **Back Annotation**

| Title                                 | Summary                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Development System<br>Reference Guide | Describes Xilinx® implementation tools and design flows, including the hierarchical flows such as Incremental Design, Modular Design, and Partial Reconfiguration.                                                                                                                                                                                                                              |

|                                       | • Includes reference information for Xilinx FPGA and CPLD command line tools, including syntax, input files, output files, and options.                                                                                                                                                                                                                                                         |

|                                       | Note: See the "NetGen" chapter for information on back annotation.                                                                                                                                                                                                                                                                                                                              |

| EDK Supplemental Information          | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze™ and the IBM® PowerPC® processors</li> <li>Includes information on core templates and Xilinx® device drivers</li> </ul>                                                                                                                                           |

| ISE Help                              | <ul> <li>Provides an overview of the Xilinx® Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul> |

### **Xilinx Device Programming**

| Title                                                                                                                            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ChipScope Documentation  Note: ChipScope Pro is one of the Optional Design Tools that can be purchased by clicking Online Store. | <ul> <li>Explains how to use the ChipScope™ Pro Core Generator™ tool to generate ChipScope Pro cores and add them to an FPGA design</li> <li>Explains how to use the ChipScope Pro Core Inserter tool to insert cores into a post-synthesis netlist without disturbing the hardware description language (HDL) source code</li> <li>Explains how to use the ChipScope Pro Analyzer tool to perform incircuit verification (also known as on-chip debugging), including how to view data and interact with ChipScope Pro cores, how to create bitstreams that are compatible with the ChipScope Pro JTAG download function, and how to download bitstreams to an FPGA using JTAG</li> </ul> |

| Data Sheets                                                                                                                      | <ul> <li>Describes the Xilinx® device families</li> <li>Provides device ordering information</li> <li>Includes detailed functional descriptions, electrical and performance characteristics, and pinout and package information</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EDK Supplemental Information                                                                                                     | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze™ and the IBM® PowerPC® processors</li> <li>Includes information on core templates and Xilinx® device drivers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Hardware User Guides                                                                                                             | <ul> <li>Describes the function and operation of Virtex™-II and Virtex-II Pro™ devices, including information on the RocketIO™ transceiver and IBM® PowerPC® processor</li> <li>Describes how to achieve maximum density and performance using the special features of the devices</li> <li>Includes information on FPGA configuration techniques and printed circuit board (PCB) design considerations</li> </ul>                                                                                                                                                                                                                                                                         |

| iMPACT Help                                                                                                                      | <ul> <li>Explains how to use the iMPACT graphical user interface</li> <li>Describes how to download bitstreams to an FPGA or CPLD using a Xilinx Parallel Cable III, Parallel Cable IV, MultiLINX™ Cable, or MultiPRO Desktop Tool</li> <li>Describes how to read back and verify design configuration data and how to perform functional tests on any device</li> <li>Describes how to generate programmable read-only memory (PROM) programming files and programming files using Xilinx System ACE™, a configuration environment that allows space-efficient, pre-engineered, high-density configuration solutions for systems with multiple FPGAs</li> </ul>                           |

| ISE Help                                                                                                                         | <ul> <li>Provides an overview of the Xilinx® Integrated Software Environment (ISE), including design flow information</li> <li>Explains how to create, define, and compile your FPGA or CPLD design using the suite of ISE tools available from the Project Navigator</li> <li>Describes what's new in the software release and how to migrate past projects to the current software</li> </ul>                                                                                                                                                                                                                                                                                            |